From late-September, and all through October, I completed breadboarding several new transistor circuit designs. The goal here was to build out a fuller complement of designs, essentially adding to my library of circuits that enable or are adaptable for the construction of a wide variety of synthesizer modules. This development is also necessary so as to conclude best ways to create PCBs. It's taken a little while to transcribe my laboratory notebook entries into easier-to-read schematics, but here are some of them.

There are three circuits described in this post:

- A new Type V2A DC Amplifier, intended as a control voltage adder and sound mixer.

- A new Type F1 DC Buffer, intended as a high-bandwidth analog line driver for 600Ω or higher loads,with higher input impedance.

- A test circuit for a 32.768 KHz local oscillator and mixer, for frequency and waveform synthesis.

An important design I wanted to complete was a DC Amplifier adder in the spirit of my previous Type V2 DC Amplifier, but with certain improvements, and broader application in mind. The idea here was to enable accurate control voltage summation, and differential summation, for overall gains of perhaps -1, or -2. Another application is for precision attenuation, such as might be used with antilog generators. Like an op amp, but with smaller parts count, because the gain range is reduced, and the output can be seen as linking to an internal circuit, rather than requiring an all-purpose potentially high-current output. In other words, a circuit design that would not require a full-blown op amp, such as the Type X1 DC Amplifier, which was a real discrete op amp that offers higher loop gain, but it has a bit higher complexity, and larger parts count.

Improvements wanted over the Type V2 DC Amplifier included larger voltage swing for small gains (-1 to -2) into loads of 2kΩ-10kΩ, which typify expected following circuits. There was also a need for higher bandwidth, since some circuit applications could have audio-frequency control voltages for modulation. Also desirable was a non-inverting output option for AC-coupled use in audio volume mixer applications. There was also a goal of employing more common transistors like 2N3904 in the differential pair role, because of their higher bandwidth contrasted with the higher-β devices like the 2N5088 or 2N5961. Also note that no transistor matching is done in this circuit design. The situation for low voltage gains, where there is already a variable control voltage from a front-panel potentiometer that is summed with a control voltage from an input jack, means that small offset voltages are basically irrelevant. What is required is sufficient DC gain, to allow gain accuracy for summations, so that precision control voltage relationships are maintained (e.g. control voltage ratios, like 2:1, not absolute voltage values). As may be needed for pitch control applications, this high-precision can be enhanced using 0.1% precision resistors in the external summing and feedback circuit.

- The Vos to the inverting output was ≤ 10mV, without any transistor selection.

- Hard undistorted voltage swing limit under (dual) 2kΩ loads was 18.4Vpp (±9.2V). A little more work could have gone into obtaining ±10V, but this much swing really isn't generally needed for the synthesizer internal paths, and in any case they are not 600Ω loads. 2kΩ is a proxy for an internal load, and often may be higher.

- The amplifier does require simple AC compensation as tested on a pad-per-hole breadboard. The transistors used are high gain devices, prone to oscillation without adequate compensation. A gain stability capacitor of 12pF is necessary for the feedback resistor in a -1/+1 gain configuration. In other application circuits, a RC snubber between the differential pair collectors may be used.

- An additional matching 12pF capacitor for the non-inverting voltage divider enabled really good CMRR for higher audio frequencies with the -1/+1 adder-subtractor. At DC and low frequencies ≤ 100 Hz, CMRR was approximately -54dB.

- Square wave response was abberation free under full load at 20 kHz, and of very clean RC shape.

- Sinusoidal FPBW under load was 144 kHz.

- The non-inverting output has more DC voltage shift, because it's not under a negative feedback loop, and it's subject to random ∆Vbe. However, per the goals, this was sufficiently small (≤ 100 mV), and dynamic range preserving, so as to enable an intended AC-coupled output application.

Some exemplary scope fotos for the Type V2A DC Amplifier follow, with 100kΩ 1% gain programming resistors for gain of ±1 at two outputs, and 2kΩ loads.

1 kHz I/O characteristics, with gains of ±1, showing the alignment of the inverting output to the input, and a small Vos shift of the non-inverting output.

Ruler flat large signal swing triangle wave output at 1KHz.

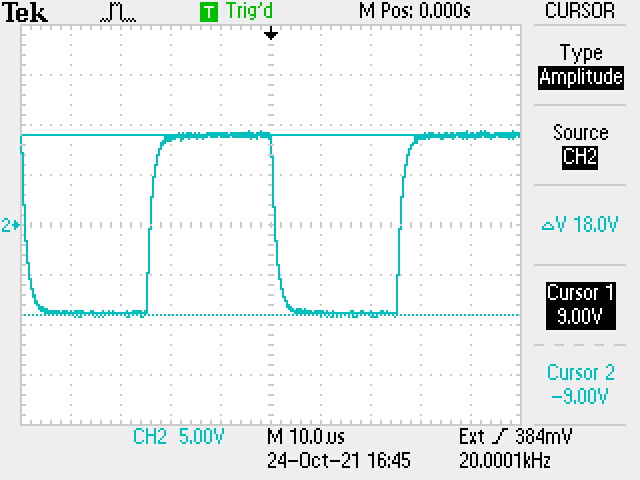

18Vpp square wave signal at 20 kHz with very clean pulse dynamics.

20 kHz pulse risetime.

20 kHz pulse falltime.

A 10 Hz ±5V input signal (YEL) applied to both ±inputs, showing the differential gain for CMRR (CYN). The (VIO) trace is an AC-coupled view of the Q2/Q3 emitter junction.

10Vpp 144 KHz input, with inverting output signal -3dB down into 2kΩ load.

The next circuit was an augmentation over the previous Type E2 and E2A transistor line drivers, to enable wider bandwidth, higher input impedance, and higher output current drive for 600Ω loads with a bit more than ±5.0V at the load, with some headroom.

The basic trick here was to take the Type E2 circuit design, replacing the 4.02kΩ 1% emitter resistors with complementary current sources instead. This circuit satisified the goals, with some provisos, that hone toward the intended application. These are described next.

The current sources Q1/Q4 greatly increase the impedance seen at the base of each emitter follower, Q2/Q3. This circuit definitely has high-impedance, because many volts out of the output into a 600Ω load can be generated with only 60 Hz hum coupling with finger touch at the input.

Due to the difference in Vbe between the PNP Q1 and the NPN Q4, the programmed standing current varies slightly between the upper and lower half of the design, perhaps more so than the case for fixed 4.02kΩ resistors as used in the Type E2 circuit. This situation results in a free-floating shift in input Vos, for some applications. For this reason, a 10kΩ shunt resistor is shown at the input on the other side of the 750Ω input resistors (which disallow AC signal feedback that cause VHF oscillation that emitter followers are known for).

The shunt resistor nails things down for DC input, but would seem to destroy some of the high-impedance benefit. The high-impedance can be maintained though without a shunt resistor for applications where the line driver is contained within a negative feedback loop. For example, in transconductance-controlled ramp generation for envelope generators.

For DC circuit applications not under feedback, the 10kΩ shunt resistor sets the Vos extremely close to 0V, without any transistor selection whatsoever. For these applications, the bandwidth and current drive are preserved. This might include buffering waveform generation and signal processing circuits.

Some scope fotos of the Type F1 DC Buffer now follow.

1 kHz sine wave 10Vpp input providing 5Vpp output into 600Ω load.

1 kHz triwave.

Ruler flat 1 kHz square wave.

5Vpp output 20 kHZ squarewave into 600Ω load with very minor amplitude attenuation.

10Vpp input and 5Vpp output risetime for 20 kHz pulse -- note change in scale for time/div!

10Vpp input and 5Vpp output falltime, also at 25 ns/div.

Output load changed to 10kΩ, circuit delivers clean 200 kHz squarewaves at ≈20Vpp.

10 kΩ load again, but 2 MHz sinewave output < 20Vpp, but close, with very slight phase shift.

The next circuit is a work-in-process, for a very different technique for frequency and waveform synthesis in music synthesizers. This approach will be delineated in a more in a later post, after more development. The basic conceptual technique worked extremely well, with even a somewhat crude implementation. For now, this conceptual technique will be described. Some similar work from 2017 is described in the Down-Conversion Frequency Synthesis post.

The concept is simple: Provide a 1st local oscillator signal source that is an ultrasonic sinusoidal source, then use a squarewave VCO as a 2nd local oscillator to drive a frequency mixer that downconverts the ultrasonic waveform into the audio band.

Why do this? Because with a sinusoidal source of high spectral purity, the products from frequency mixing fall directly into the audio band and far outside it, esp. for very low frequencies. A low pass filter following the mixer provides this separation for a clean baseband (audio) signal. A squarewave 2nd local oscillator can then generate any musically useful audio pitch, by mixing against the 1st local oscillator with a switching-oriented frequency mixer, and all of the harmonics represented by the squarewave source are massively surpressed. This is a frequency heterodyning technique adapted from swept-frequency spectrum analyzers. A suitable sinuosoidal source is a 32.768kHz crystal oscillator, which has Q=90000. The circuit below even used a crude switching frequency mixer, and it still got rock-solid constant amplitude audio baseband signals out. Several such squarewave 2nd local oscillators could all be applied at once with similar mixers, allowing a precise direct additive audio waveform synthesis using analog means.

This is a frequency difference mixer. So the IF is audio baseband, RF is the 1st local oscillator, and LO is the 2nd local oscillator. The mixer produces the following frequencies (after the LPF): RF - LO = IF.

Of extreme importance is that the frequency range required of the 2nd local oscillator in order to obtain a very wide range audio output is less than a single octave! A 2nd local oscillator having a voltage control range of 24.576 kHz to 32.768 Khz allows a downconversion range from 0 Hz to 8192 Hz. This is about 2/3 of one single octave, allowing circuit design for extremely high linearity and precision. Which allows multiple simultaneous instances.

The test circuit below easily obtained 14 octave super clean sounding sinusoidal audio from one single 2/3 octave 2nd local oscillator. For convenience in building out this design (which only has 6 transistors!), the 2nd local oscillator was provided temporarily by my HP 33120A signal generator, and only a ±5V signal drive was used to drive the mixer LO port.

The 1st local oscillator design is adapted using the new Type V2A DC Amplifier, based on my previous work for a Leveled Sinusoidal Crystal Oscillator. Due to the inverse frequency relation for a downconversion mixer, while eventually mapping the 2nd local oscillator to a 1V/OCT system, a suitable transistor-based antilog convertor has already been developed and tested. This is the Wide-Range Stable Exponential Generator, an adaption of a circuit design from 1968.

More to come.

Comments

Post a Comment