Update 3/17/2023:

The +5V circuits do work well, but I have since decided that +15V single supply power for analog waveform generation and signal processing has several advantages. Among them are 20 years of research and development in LM3900 circuit designs. More updates in a blog post.

I've been building out and adapting various synthesizer circuit designs for +5V power operation. Using a single supply makes everything much easier to implement for a self-contained semi-modular low power Mini-Moog like synthesizer.

I've spent a lot of research and development effort on antilog circuits, over the last 23 years. This has included mixed-signal specialized A/D and D/A approaches; sampling a repetitively generated antilog voltage; antilog PWM circuits using frequency synthesizers; +15V only antilog circuits with the LM3900; and precision antilog DACs that are insensitive to CMOS switch Rds(on).

In fact, the antilog DACs really do work, but they require digital front ends and A/D conversion I don't want the complexity of, when contrasted with a pure analog antilog circuit. Also, the +15V unipolar LM3900 antilog circuits work too, but for a critical application like pitch generation they need matched PNP transistors. Otherwise the different Vt of mismatched PNP pairs fight each other, generating small ultra-low-frequency drift voltages in response to thermal activity in their environment. This drift and wander can be seen readily with a 12-bit digital scope, re-emphasizing that analog circuit design always has thermal inputs too.

For the +5V application, after trying all of the above, I decided to gave in to the majesty of the bipolar junction transistor (BJT). To get back into the groove for this design, I went to Open Music Labs, to reference the classic SDIY paper on error sources and their correction for antilog generators. I ultimately developed the +5V circuit using a NPN matched transistor pair and a +3300ppm thermistor, which will now be described.

Here's the schematic of the test design, engineering notes and characterization data index:

The only remarkable thing about about the +5V realization is how simple it turned out to be, and also how well it worked. For one thing, precision rail-to-rail CMOS op amps are virtually perfect devices. I used the Microchip Technology MPC6024-E/P quad op amp, which has 250μV offset voltage, and picoamp bias and offset currents over temperature ranges I care about. Vos drift is also quite neglible. And the LM394 super matched NPN pair is a marvelous device, having Vbe matching to 50μV, β matching, and other highly desireable characteristics for log conformance. This matched pair is less available today, but there are now clone LM394 devices like the AS394. There are also replacement alternatives available like the Linear Integrated Systems LS318, and others. As it happens, I had purchased over 100 LM394CH units more than 20 years ago, so it makes sense to finally use them!

The +5V implementation is different than a ±15V circuit. Some system engineering notes about this issue now follow.

For one thing, the control voltage input and output ranges are necessarily smaller. One key thing in the "super-mini" synthesizer design I have in mind is that the +5V voltage rail will always be precision voltage, basically generated with LDO voltage regulators having a 0.4% voltage tolerance. In fact, to prevent mode-locking and current path issues, the VCOs in the synthesizer will have individually separate LDO voltage regulators, thus isolating all VCO supply voltages from each other. So, each 5V power bus is actually +5Vref.

Op amps are devices that generally work with both positive and negative signals, so how to do that with +5V power? As was discussed in my +5V Trimless VCA work, the answer is to use a Voltage Zero Reference (VZR), nominally Vcc/2, or one-half of the +5V power supply voltage range. The idea being this allows maximum range for positive and negative voltage swing about the VZR. Other names for VZR that are analogous are virtual ground and the common mode reference voltage. The recent +5V circuit designs I'm developing make VZR a precise reference voltage relative to system ground. This is developed by a LM4040AIZ-2.5V calibrated zener reference diode, which offers +2.500V output. The reference diode is then buffered with a precision unity gain buffer op amp for low-impedance distribution to other circuit elements. In this way, all sub-circuits within the synthesizer will be using a common VZR, and thus be interoperable for all signal exchanges.

With a +2.500V VZR, calibrated against system ground, control voltages can range from 0-5V. This voltage range also can represent ±2.5V bipolar signals. As audio output a +2.500V VZR also allows plenty of signal swing for 3.47Vpp waveform signals, which are the professional audio signal level of +4dBu. The margin against clipping with +5 power relative to ground is of course much less than with a ±15V or ±24V power system. So, some care in signal handling is necessary. But widely used modular waveforms of ±5V or ±10V, or DC control voltages of 10V unipolar range, are not strictly necessary in order to construct a synthesizer. Also, a synthesizer is not necessarily an exercise in audiophile grade performance, in multiple dimensions. For example audio distortion is in some cases actually desired, for waveform shaping. Noise performance rivalling a spectrum analyzer is not required. A sufficiency of dynamic range, perhaps 80dB is good enough. Low voltage, low power semiconductors like CMOS op amps along with BJTs are a potent combination for synthesizer realization at +5V power.

The antilog generator accepts 0-5V inputs, which are seen as ±2.5V inputs. The generator provides outputs riding above VZR. So that's approximately a bit more than 2.5V up to 5.0V. I decided to design the circuit for a standard 10-octave range, expecting that for a 37-note synthesizer keyboard the required antilog pitch accuracy only has to be really good for a bit more than 3 octaves. Per Open Music Labs, this is easily achievable, esp. if the temperature range intended is not over the entire commecial or industrial temperature range. The 10-octave range is compressed by having the representation be 0.5V/octave, instead of 1V/octave. Therefore, a ΔV of 5V works out to be 10 octaves.

Quick notes on Theory of Operation. Op amp U1A buffers the LM4040 reference to provide low-impedance ("stiff") VZR of 2.500V to the rest of the circuit. In the circuit, at a nominal 300°K, op amp U1B compresses the input 0-5V range to 2.500V ± 90 mV to the base of Q1A. The tolerance for the thermistor is handled by the 5kΩ scale trimming pot, which then sets the full-scale range to 5.00V, through read-out op amp U1C. Op amp U1D regulates a 10μA reference current through the matched pair, which represents the mid-scale antilog output (e.g. the output for a control voltage of "0" at VZR, or 2.5V). When the control voltage input is increased to +5V, the current through Q1B increases to 32x that of the 10μA reference current, or 325.5 μA. With a resistor of 7.68kΩ 1% in the feedback loop of the read out op amp U1C, for +5V input, and 2.500V - 90mV at the base of Q1A, the output will develop 2.500V + (325.5 μA ∙ 7.68kΩ) which is very close to 5V full scale.

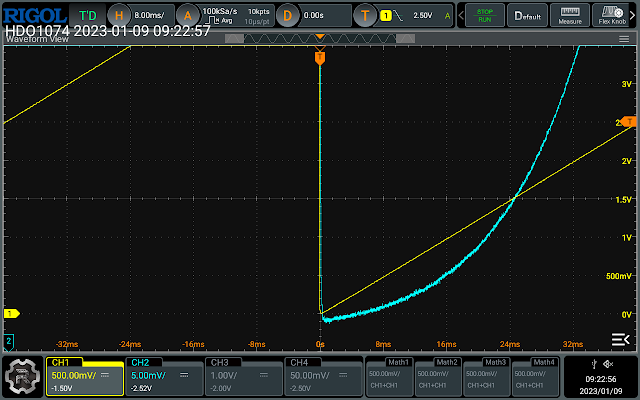

The design was remarkably temperature stable without even having the thermistor thermally bonded to the LM394. I didn't really have capabilities for comprehensive thermal testing. This test design was more about did I get the topology and component values correct for +5V operation. After calibrating the scale trimmer to yield +5.00V full-scale, the antilog conformance to 0.5V/octave was quite good. The actual PCB realization would provide thermal coupling. Example scope fotos are next.

.JPG)

Comments

Post a Comment